Record du monde : transistor GAAFET à 5nm d'IBM, Samsung et GlobalFoundries

19 juin 2017

sur

sur

Partenaires de recherche, IBM, Samsung et GlobalFoundries ont développé un processus industriel en première mondiale pour construire des transistors à base de nanofeuilles de silicium, ouvrant ainsi la voie à la production de puces électroniques en 5 nm. Le circuit intégré en 5 nm d’IBM est également le premier fondé sur la topologie de transistors GAA (Gate-All-Around) et probablement la première véritable application du procédé de lithographie EUV (extrême ultraviolet).

Les transistors GAAFET constituent une nouvelle étape, après les FinFET Tri-Gate qui bénéficient d'une largeur de structure de 22 et 14 nm, mais ne peuvent être miniaturisés au-delà de 7 nm. En comparaison, les GAAFET devraient permettre de réaliser des structures de 3 nm. Qui a dit que la loi de Moore était dépassée ? Vraiment ?

Jusqu'ici, la fabrication de transistors consistait à superposer différents matériaux sur des circuits intégrés. Pour autant, avec la miniaturisation permanente des structures, il devient de plus en plus difficile de produire des transistors 2D possédant des propriétés satisfaisantes (vitesse de commutation et courant de fuite). Le nombre d'atomes intervenant dans la circulation du courant électrique est de plus en plus faible.

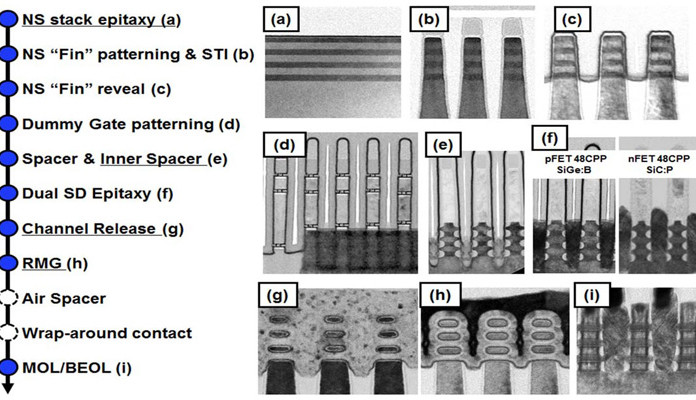

D'où l'idée d'intégrer une troisième dimension qui a donné lieu au procédé FinFET, dans lequel un « aileron » émerge du substrat et contribue donc au semi-conducteur par les atomes qu'il contient. La structure obtenue est mince, ce qui permet d'y associer de nombreux transistors. En revanche, les GAAFET sont essentiellement des structures 2D superposées, mais bénéficiant d'une topologie 3D. Il s'agit ici d'un FinFET renversé où les ailerons ne sont plus perpendiculaires au substrat, mais posés à plat. Un aileron peut être considéré comme un nanoconducteur ou une nanocouche reliant le drain et la source. Avec les GAAFET d’IBM, trois de ces couches sont superposées, et la grille comble les interstices, ce qui offre une zone de grille et un volume de canal généreux, avec, à la clé, d'excellentes propriétés électriques.

Les transistors GAAFET constituent une nouvelle étape, après les FinFET Tri-Gate qui bénéficient d'une largeur de structure de 22 et 14 nm, mais ne peuvent être miniaturisés au-delà de 7 nm. En comparaison, les GAAFET devraient permettre de réaliser des structures de 3 nm. Qui a dit que la loi de Moore était dépassée ? Vraiment ?

Jusqu'ici, la fabrication de transistors consistait à superposer différents matériaux sur des circuits intégrés. Pour autant, avec la miniaturisation permanente des structures, il devient de plus en plus difficile de produire des transistors 2D possédant des propriétés satisfaisantes (vitesse de commutation et courant de fuite). Le nombre d'atomes intervenant dans la circulation du courant électrique est de plus en plus faible.

D'où l'idée d'intégrer une troisième dimension qui a donné lieu au procédé FinFET, dans lequel un « aileron » émerge du substrat et contribue donc au semi-conducteur par les atomes qu'il contient. La structure obtenue est mince, ce qui permet d'y associer de nombreux transistors. En revanche, les GAAFET sont essentiellement des structures 2D superposées, mais bénéficiant d'une topologie 3D. Il s'agit ici d'un FinFET renversé où les ailerons ne sont plus perpendiculaires au substrat, mais posés à plat. Un aileron peut être considéré comme un nanoconducteur ou une nanocouche reliant le drain et la source. Avec les GAAFET d’IBM, trois de ces couches sont superposées, et la grille comble les interstices, ce qui offre une zone de grille et un volume de canal généreux, avec, à la clé, d'excellentes propriétés électriques.

Lire l'article complet

Hide full article

Discussion (0 commentaire(s))