Le retour des petits circuits – 17e épisode : métronome analogique

sur

Métronome électronique

idée: Elex

Le battement du métronome est régulier, mais contrairement à ce que l'on pourrait croire, ce n'est ni un tac-tac-tac ni un tic-tic-tic, mais bien une alternance de tic et de tac, perçue comme plus musicale (on parle d'arsis et de thesis). Ici le volume de l'un et de l'autre son réglables séparément.

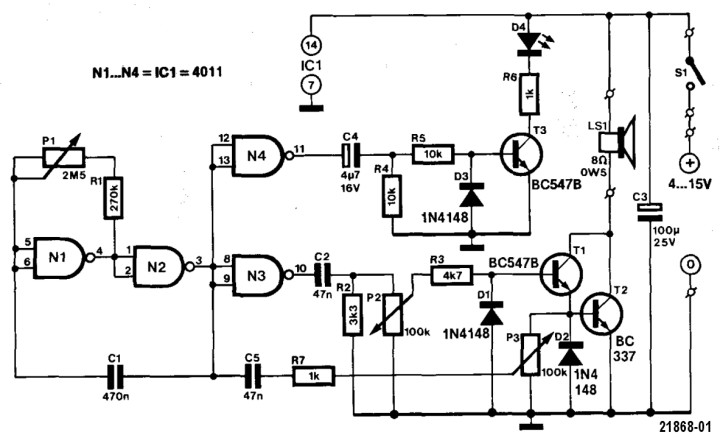

Le cœur du schéma ci-dessous est un générateur de signal carré formé de N1 et N2, deux opérateurs logiques CMOS NON-ET ou NAND en anglais, intégrés dans le circuit (CD)4011. La fréquence du signal carré est réglée par le potentiomètre P1.

D’autre part notre signal carré passe par l’inverseur N3 et le différentiateur C2/R2/P2 pour arriver, via le potentiomètre de volume, à la base d'un Darlington T1/T2. Ce couple de transistors introduit un gain considérable de sorte que l'impulsion de sortie du différentiateur se traduit par un claquement sonore de la membrane du haut-parleur. C’est notre tic !

L'ilpulsion carrée non inversée issu de N2 passe aussi par un troisième différenciateur pour atteindre, via le potentiomètre P3, la base de T2. Comme ce signal-là n’est amplifié que par un seul transistor et non par un vigoureux Darlington, il produit un claquement moins sonore. Ce sera le tac de notre métronome qui fait donc alternativement tic – tac - tic – tac etc.

Ce circuit est facile à assembler sur un morceau de circuit à pastilles ou sur une plaque d’expérimentation à ressorts ; utilisez un support de circuit intégré pour le 4011 et manipulez-le avec précaution : certes, aujourd’hui les circuits intégrés CMOS ne sont plus aussi vulnérables qu’ils l’étaient, ils restent néanmoins plus sensibles aux décharges électrostatiques que les autres semi-conducteurs.

Discussion (1 commentaire(s))