Des transistors 4D

10 décembre 2013

sur

sur

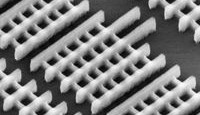

Montera-t-il sur scène en agitant ses trois papattes pour saluer la foule ? On l'ignore encore. En tout cas il est annoncé comme vedette de la conférence IEDM (International Electron Devices Meeting) qui se tiendra à San Francisco la semaine prochaine. Pour l'instant, personne n'a encore pu lui tirer le portrait. Lui, c'est le transistor 4D, un nouveau type de transistor créé par une équipe déjà à l'origine des transistors 3D, ces transistors tridimensionnels qui ont permis une plus forte densité des puces et offert des gains de performance supérieurs à ceux de la génération « plate ». Vers quelle dimension tordue de l'espace pointe donc le quatrième D de ce transistor 4D ? Tendons le micro au professeur Ye, un des pères de ces nouveaux composants :

« Une maison de plain-pied peut accueillir un certain nombre de personnes, mais bien plus si vous ajoutez des étages ; c'est la même chose avec les transistors, les empiler permet d'obtenir plus de courant et des vitesses de traitement plus rapides. Cette technique d'empilement ajoute une nouvelle dimension, alors je les ai appelés 4D. »

Voilà. Rien de bien nouveau sous le soleil, finalement. Les transistors 4D sont donc des transistors 3D qui peuvent être assemblés verticalement et en parallèle. Il y a tout de même un peu plus. À la différence des nanofils en silicium des transistors 3D, ceux des transistors 4D sont en arséniure de gallium et d'indium, un matériau dont la mobilité électronique intrinsèque est beaucoup plus grande que celle du silicium, d'où une plus grande intensité du courant lorsque le transistor est en mode actif, et une vitesse de commutation plus élevée entre les états actif et éteint. Autre différence, la nouvelle couche diélectrique (isolante) ultrafine qui recouvre les nanofils des transistors 4D empêche les fuites de courant lorsque le transistor est en mode éteint. C'est d'ailleurs cet isolant ultrafin qui a permis aux chercheurs de fabriquer par dépôt de couches minces des transistors 4D avec des grilles de seulement 20 nanomètres de large, une étape décisive selon le professeur Ye. Yeah.

« Une maison de plain-pied peut accueillir un certain nombre de personnes, mais bien plus si vous ajoutez des étages ; c'est la même chose avec les transistors, les empiler permet d'obtenir plus de courant et des vitesses de traitement plus rapides. Cette technique d'empilement ajoute une nouvelle dimension, alors je les ai appelés 4D. »

Voilà. Rien de bien nouveau sous le soleil, finalement. Les transistors 4D sont donc des transistors 3D qui peuvent être assemblés verticalement et en parallèle. Il y a tout de même un peu plus. À la différence des nanofils en silicium des transistors 3D, ceux des transistors 4D sont en arséniure de gallium et d'indium, un matériau dont la mobilité électronique intrinsèque est beaucoup plus grande que celle du silicium, d'où une plus grande intensité du courant lorsque le transistor est en mode actif, et une vitesse de commutation plus élevée entre les états actif et éteint. Autre différence, la nouvelle couche diélectrique (isolante) ultrafine qui recouvre les nanofils des transistors 4D empêche les fuites de courant lorsque le transistor est en mode éteint. C'est d'ailleurs cet isolant ultrafin qui a permis aux chercheurs de fabriquer par dépôt de couches minces des transistors 4D avec des grilles de seulement 20 nanomètres de large, une étape décisive selon le professeur Ye. Yeah.

Lire l'article complet

Hide full article

Discussion (0 commentaire(s))